# pcSQUID<sup>TM</sup> User's Manual

**PCS102** Control Software

Programmable Feedback Loop Model PFL-102

Personal Computer Interfaces Models PCI-100 and PCI-1000

STAR Cryoelectronics

25 Bisbee Court, Suite A Santa Fe, NM 87508 U. S. A.

# **Table of Contents**

| Rev  | rision | Record                                                      | <i>v</i> |

|------|--------|-------------------------------------------------------------|----------|

| Tec  | hnica  | ll Support                                                  | <i>v</i> |

| Wai  | rranty | /                                                           | vi       |

| Safe | ety P  | recautions                                                  | vi       |

| 1    | STA    | AR Cryoelectronics' PC-Based DC SQUID Electronics: Overview | 1        |

| 2    | Inst   | allation and Setup                                          | 3        |

| 2    | .1     | Unpacking and Inspection                                    | 3        |

| 2    | .2     | Additional Equipment Required                               | 4        |

| 2    | .3     | Hardware Installation and Configuration                     | 4        |

| 2    | .4     | Software Installation and Configuration                     | 6        |

| 3    | Ope    | eration                                                     | 11       |

| 3    | .1     | Two-Stage SQUID Amplifier Overview                          | 11       |

| 3    | .2     | Tuning the Output Array                                     | 13       |

| 3    | .3     | Tuning the Input SQUID                                      | 20       |

| 4    | PCS    | S102 Control Software                                       | 24       |

| 4    | .1     | Operating the Software: A Brief Look                        | 24       |

| 4    | .2     | Main Panel Functions                                        | 27       |

| 4    | .3     | PCI Panel Functions                                         | 34       |

| 4    | .4     | List of Hot-Keys for the PCS102 Control Software            | 39       |

| 5    | Mo     | del PFL-102 Programmable Feedback Loop                      | 41       |

| 5    | .1     | Circuit Description                                         | 41       |

| 5    | .2     | Changing the Address of a PFL-102                           | 45       |

| 5    | .3     | Changing the PFL-102 Output Configuration                   | 46       |

| 5    | .4     | Adjusting the Preamplifier Balance                          | 47       |

| 5    | .5     | Adjusting the Common Mode Rejection                         | 49       |

| 5    | .6     | Modifying the SQUID and Array Bias Ranges                   | 50       |

| 5    | .7     | Modifying the SQUID and Array Flux Bias Ranges              | 51       |

| 5    | .8     | PFL-102 Connector Pinouts                                   | 54       |

| 5    | .9     | Specifications, Programmable Feedback Loop Model PFL-102    | 55       |

| 6    | Mo     | del PCI-100 Single Channel PC Interface                     | 56       |

| 5.1         | PCI-100 Front Panel Description                             | 56                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2         | PCI-100 Rear Panel Description                              | 57                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.3         | Changing the Filter in the PCI-100                          | 57                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4         | PCI-100 Connector Pinouts                                   | 59                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.5         | PCI-100 Specifications                                      | 61                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mod         | lel PCI-1000 Multichannel PC Interface                      | 62                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>'</b> .1 | PCI-1000 Front Panel Description                            | 62                                                                                                                                                                                                                                                                                                                                                                                                   |

| .2          | PCI-1000 Rear Panel Description                             | 63                                                                                                                                                                                                                                                                                                                                                                                                   |

| '.3         | Changing the Address and Filters in the PCI-1000            | 64                                                                                                                                                                                                                                                                                                                                                                                                   |

| '.4         | PCI-1000 Connector Pinouts                                  | 66                                                                                                                                                                                                                                                                                                                                                                                                   |

| '.5         | PCI-1000 Specifications                                     | 70                                                                                                                                                                                                                                                                                                                                                                                                   |

| STA         | R Cryoelectronics Serial Control Code                       | 71                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 5.2<br>5.3<br>5.4<br>5.5<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5 | <ul> <li>PCI-100 Rear Panel Description</li> <li>Changing the Filter in the PCI-100</li> <li>PCI-100 Connector Pinouts</li> <li>PCI-100 Specifications</li> <li>Model PCI-1000 Multichannel PC Interface</li> <li>PCI-1000 Front Panel Description</li> <li>PCI-1000 Rear Panel Description</li> <li>Changing the Address and Filters in the PCI-1000</li> <li>PCI-1000 Connector Pinouts</li> </ul> |

| <b>Revision Record</b> |          |                                                                                   |

|------------------------|----------|-----------------------------------------------------------------------------------|

| Date                   | Revision | Description                                                                       |

| October 30, 2002       | 1.0      | First Release                                                                     |

| October 21, 2003       | 1.1      | Added flux offset circuit description                                             |

| March 5, 2004          | 1.2      | Updated for SA1 <i>xx</i> /SA6 <i>xx</i> amplifiers;<br>improved heater operation |

© 2002 – 2004 by STAR Cryoelectronics, LLC, Santa Fe, NM 87508

All rights reserved. No part of this manual may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission of STAR Cryoelectronics.

STAR Cryoelectronics reserves the right to change the functions, features, or specifications of its products at any time, without notice.

The PFL102 Control Software was developed using National Instruments' LabWindows/CVI. Copyright National Instruments Corporation. All rights reserved.

# TECHNICAL SUPPORT

If you have any questions or comments about this product or other products from STAR Cryoelectronics, please contact:

| STAR Cryoelectronics                                |                     |  |  |

|-----------------------------------------------------|---------------------|--|--|

| 25-A Bisbee Court<br>Santa Fe, NM 87508<br>U. S. A. |                     |  |  |

| http://www.starcryo.com/                            |                     |  |  |

| Technical Support:                                  |                     |  |  |

| Tel.:                                               | (505) 424-6454      |  |  |

| FAX:                                                | FAX: (505) 424-8225 |  |  |

| Email: info@starcryo.com                            |                     |  |  |

## WARRANTY

### **STAR Cryoelectronics Limited Warranty**

STAR Cryoelectronics warrants this product for a period of twelve (12) months from date of original shipment to the customer. Any part found to be defective in material or workmanship during the warranty period will be repaired or replaced without charge to the owner. Prior to returning the instrument for repair, authorization must be obtained from STAR Cryoelectronics or an authorized STAR Cryoelectronics service agent. All repairs will be warranted for only the remaining portion of the original warranty, plus the time between receipt of the instrument at STAR Cryoelectronics and its return to the owner.

This warranty is limited to STAR Cryoelectronics products that are purchased directly from STAR Cryoelectronics, its OEM suppliers, or it's authorized sales representatives. It does not apply to damage caused by accident, misuse, fire, flood or acts of God, or from failure to properly install, operate, or maintain the product in accordance with the printed instructions provided.

This warranty is in lieu of any other warranties, expressed or implied, including merchantability or fitness for purpose, which are expressly excluded. The owner agrees that STAR Cryoelectronics' liability with respect to this product shall be as set forth in this warranty, and incidental or consequential damages are expressly excluded.

# SAFETY PRECAUTIONS

Do not remove product covers or panels except for modifications as specified in this manual.

Do not operate without all covers and panels in place.

Do not attempt to repair, adjust, or modify the instrument, except for modifications as specified in this manual. This could cause nullification of any warranty. For service, return the instrument to STAR Cryoelectronics or any authorized representative.

Do not operate this instrument in a volatile environment, such as in the presence of any flammable gases or fumes.

# 1 STAR Cryoelectronics' PC-Based DC SQUID Electronics: Overview

## A Revolution in SQUID Instrumentation!

STAR Cryoelectronics' PC-based SQUID readout electronics represent a breakthrough in dc SQUID instrumentation technology. This revolutionary architecture brings the power of your PC and the flexibility of virtual instrumentation to SQUID control and data acquisition. The easy-to-use user interface for Microsoft Windows<sup>™</sup> puts the SQUID control on your computer right where you want it - fully integrated with your data acquisition and analysis tools.

## Advanced Programmable Feedback Loop

The high-speed Programmable Feedback Loop Model PFL-102 is designed to control two-stage SQUID amplifiers and single-stage series SQUID array amplifiers, and offers wide bandwidth (>1 MHz) and high slew rate (>1 M $\Phi_0$ /sec) operation. The PFL-102 includes two independent bias drive circuits, one for the voltage-biased low-noise input stage, one for the series SQUID array output stage. Two independent feedback circuits are available, allowing the feedback to be coupled to the input stage or to the output stage for locked loop operation. All drive signals and feedback loop parameters may be configured remotely via software and a personal computer. The compact and low-power design simplifies multichannel and portable operation.

## PC Interface Unit

The PC Interface (PCI) unit is controlled by a personal computer via the RS-232 or parallel port. All digital control signals to the Programmable Feedback Loop are generated by a STAR Cryoelectronics Serial Control Code (SCC) transmitter in the PC Interface unit. The Model PCI-1000 can operate up to 8 channels, while the low-cost Model PCI-100 is ideal for single-channel applications. Each model may be configured for master or slave mode for multichannel applications. The analog output signals from the Programmable Feedback Loops are available at the PC Interface unit via BNC front-panel connectors, either wideband or optional low-pass filtered with user-selected cutoff frequencies.

## Control Software for Windows<sup>™</sup>

The pcSQUID<sup>™</sup> Control Software makes dc SQUID operation easy for the first-time user, yet allows the expert complete control over the full power and features of the Programmable Feedback Loop. The graphical user interface for Microsoft Windows<sup>™</sup> displays multichannel information at a glance. Three basic modules are used to control and configure the components of the system: The SQUID Control Module is used to individually configure the PFL units for each sensor, while the PCI Module provides control over the PCI-1000 multichannel PC Interface unit.

## About this Manual

This manual describes the setup, operation, and technical specifications of the pcSQUID<sup>TM</sup> system. Section 2 describes the installation and setup of your hardware and software, including important configuration instructions. Section 3 presents a brief tutorial on the operation of the pcSQUID<sup>TM</sup> system which is geared toward users having some familiarity with SQUIDs and SQUID electronics. It is designed to get you up-and-running quickly. In Section 4, we describe in detail the pcSQUID<sup>TM</sup> control software, its operation, and the function of all its controls and options. Section 5 focuses on the Programmable Feedback Loop, primarily on a technical

description of its features and operation. Sections 6 and 7 describe the PC Interface units, the PCI-100 for single-channel operation and the PCI-1000 for multichannel operation, respectively. Finally, in Section 8 we present a brief overview of the STAR Cryoelectronics Serial Control Code (SCC), a serial communications protocol developed especially for use with SQUID systems.

## Thank You!

Thank you for purchasing pcSQUID<sup>TM</sup>, a popular member of STAR Cryoelectronics' family of advanced dc SQUIDs and instrumentation electronics. We hope you will find it extremely powerful and flexible, yet easy to use and integrate with your application. And remember, the experienced technical staff at STAR Cryoelectronics are always available to discuss your particular application or needs.

## 2 Installation and Setup

STAR Cryoelectronics' pcSQUID<sup>™</sup> System is available in two pre-configured packages for either single- or multichannel applications. Each basic package includes all necessary cabling for a complete one-channel installation (not including sensor and cryocable).

## 2.1 Unpacking and Inspection

Prior to unpacking your PC-based electronics system, inspect the shipping carton(s) for any signs of damage that may have occurred during shipment. If damage is observed, notify the carrier immediately to allow for a possible insurance claim.

The following sections list the items included with the single-channel and multichannel PCbased SQUID electronics systems. If any items are missing, notify your STAR Cryoelectronics representative immediately.

## 2.1.1 Model PC-102 Single-Channel High-Speed dc SQUID Electronics

This package includes:

| PCI-100   | Single-channel PC Interface with Integral STAR Cryoelectronics Serial<br>Control Code Transmitter         |

|-----------|-----------------------------------------------------------------------------------------------------------|

| PS-115    | Power Source, 115 VAC, 60 Hz, wall plug-in (or 220V international version)                                |

| LP-5      | Low-Pass Filter, 5 kHz, 4-pole Butterworth (usually factory installed in the PCI-100 at time of shipment) |

| CBL-25P2  | Interface Cable, 25-pin M/F, 2 meters                                                                     |

| PFL-102   | Single-Channel Programmable Feedback Loop for two-stage SQUID amplifiers                                  |

| CBL-9P10  | PFL Cable, Double-Shielded, 9-pin M/F, 10 feet                                                            |

| CBL-LB10  | PFL output cable, 1-pin LEMO to BNC, 10 feet                                                              |

| PCS102    | Control Software for Microsoft Windows <sup>TM</sup>                                                      |

| UM-PCS102 | User's Manual                                                                                             |

|           | Cryogenic Cable (optional)                                                                                |

|           | dc SQUID sensor (optional)                                                                                |

2.1.2 Model PC-1000 Basic Multichannel High-Speed dc SQUID Electronics

This package includes:

- PCI-1000 Multichannel PC Interface with Integral STAR Cryoelectronics Serial Control Code Transmitter; AC power cord and fuses installed in the Power Entry Module (user selectable for 110 or 220 VAC, 50/60 Hz; factory configured for 120 VAC operation unless specified otherwise)

- CBL-25P2 Interface Cable, 25-pin M/F, 2 meters

| PFL-102   | Single-Channel Programmable Feedback Loop for two-stage SQUID amplifiers |

|-----------|--------------------------------------------------------------------------|

| CBL-9P10  | PFL Cable, Double-Shielded, 9-pin M/F, 10 feet                           |

| CBL-LB10  | PFL output cable, 1-pin LEMO to BNC, 10 feet                             |

| PCS102    | Control Software for Microsoft Windows <sup>TM</sup>                     |

| UM-PCS102 | User's Manual                                                            |

In addition to the above, the following options may be shipped along with the basic multichannel system.

Model LP-SET Low-Pass Filter Set for PCI-1000 (Optional). Includes:

3 kHz, 6 kHz, 15 kHz and 30 kHz 4-pole Butterworth Low-Pass Filters (factory installed in the PCI-1000 at time of shipment if ordered; user installed if purchased separately)

Model PC-1000A Additional Channel add-on package (Optional). Includes:

PFL-102 Single-Channel Programmable Feedback Loop for two-stage SQUID amplifiers

CBL-9P10 PFL Cable, Double-Shielded, 9-pin M/F, 10 feet

## 2.2 Additional Equipment Required

The STAR Cryoelectronics PC-based SQUID electronics are designed to operate with an IBMcompatible personal computer running Microsoft Windows<sup>TM</sup> XP, 2k, 9x, or NT. To view the SQUID output signal, you will need an oscilloscope and BNC cables. If you are using a PCI-100 system, you will also need a test signal generator and additional BNC cables.

If you are not using dc SQUIDs and cryocables provided by STAR Cryoelectronics, you will need an appropriate dc SQUID sensor and cryogenic cabling that mates with the 14-pin LEMO plug on the Model PFL-102 Programmable Feedback Loop. The appropriate mating connectors may be purchased from STAR Cryoelectronics.

## 2.3 Hardware Installation and Configuration

# 2.3.1 Configuring the Hardware Addresses

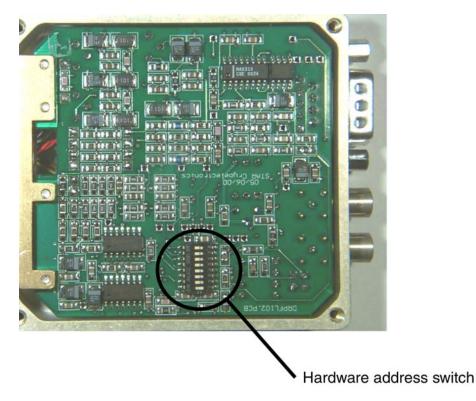

For proper operation, each PFL-102 and PCI-1000 must be properly configured with the correct hardware address. The PFL-102 units usually are factory configured with address 1 and the PCI-1000 units with address 255. For a single channel system you will not need to change the address of either the PFL or PCI units. If you purchased a multichannel system, the proper addresses are pre-configured at the factory and should not require further configuration, unless you wish to change the address of a particular channel or channels. The hardware addresses are set using DIP switches located inside the PFL-102 and PCI-1000. To access the hardware address switch, the cover of the unit must be removed. For detailed instructions, please refer to Section 5.2 (for PFL-102), or Section 7.3 (for PCI-1000). The PCI-100 is not addressable and needs no adjustment.

The addressing scheme is as follows: Available addresses range from 1 to 255. The address of each PFL-102 must correspond to its channel number, starting with address 1 for Channel 1 and

increasing sequentially. The first PCI unit (Channels 1 to 8) should be set to address 255, the second PCI unit (Channels 9 to 16) to address 254, etc. The PCI unit addresses decrease sequentially in this manner as units are added. This scheme, where the PFL-102 addresses increase starting from 1 and PCI-1000 addresses decrease starting from 255, maximizes the use of the 255 available addresses. A summary of the hardware addressing scheme is given in Table 2.1.

| Hardware                | Address |

|-------------------------|---------|

| PFL, Channel 1          | 1       |

| PFL, Channel 2          | 2       |

| :                       |         |

| PFL, Channel 9          | 9       |

| :                       |         |

| PCI-1000, Channels 1-8  | 255     |

| PCI-1000, Channels 9-16 | 254     |

| :                       |         |

Table 2.1 Required pcSQUID<sup>™</sup> hardware address settings.

## 2.3.2 Configuring the PFL-102 Analog Output

The PFL-102 is factory configured such that the SQUID amplifier output signal is available only at the WB OUT 1-pin LEMO connector on the PFL-102. A 1-pin LEMO-to-BNC adapter cable is provided to monitor the output with an oscilloscope or spectrum analyzer.

## WARNING

The wideband output should be connected only to a high impedance load such as an oscilloscope or spectrum analyzer, never to a load with an input impedance of less than 600  $\Omega$ . Connecting the wideband output to a low-impedance load will damage the output buffer amplifier in the PFL-102.

Alternately, the output signal can be routed via the 9-pin SCC INTERFACE connector and 9-pin PFL cable to the PCI unit. The output in this case is bandwidth limited to approximately 100 kHz and can be monitored at the FILTERED or WIDEBAND BNC connectors on the front panel of the PC Interface. The output signal is still available at the WB OUT 1-pin LEMO connector on the PFL-102 in this case, but the system bandwidth will be reduced. To reconfigure the PFL-102 for this output option, please see Section 5.3.

## 2.3.3 Initial Power-Up Procedure

- 1. Verify that the power switch on the PCI is in the OFF position. If you are using a PCI-100 interface, verify that the plug-in Power Source is the proper type for the voltage in your area. Plug the DIN connector into the POWER socket on the back of the PCI-100, and connect the Power Source to a grounded mains outlet. If you are using a PCI-1000 interface, inspect the voltage selector on the rear panel of the PCI-1000 and make sure it is set for the proper voltage in your area. Connect the ac power cord to the PCI-1000 and plug it into a grounded power outlet.

- 2. If you are using a PCI-100 interface, connect the female end of the 9-pin interface cable to the PFL unit and connect the male end of the 9-pin PFL cable to the FEEDBACK LOOP connector on the rear panel of the PCI-100. If you are using a PCI-1000 interface, for each channel connect the female end of the 9-pin interface cable to the PFL unit and connect the male end of the cable to the connector of the appropriate channel on the rear panel of the PCI-1000. The PCI-1000 channels must be assigned in correspondence with the hardware address of each PFL unit.

- 3. Verify that the power to the PC is turned off (if necessary, follow the manufacturer's instructions to power down the PC). Connect one end of the 25-pin interface cable to either the parallel port or RS-232C interface (an adapter may be necessary) on the PC. Connect the other end to the appropriate interface port on the rear panel of the PC interface.

- 4. If you are using more than one PCI unit, connect these additional units to their corresponding PFL unit(s) and power sources as in Steps 1 and 2 above. In Step 4, the PCI-1000 interfaced to the PC will serve as Master, and all remaining Slave PCI-1000 units must be connected together in a daisy-chain manner in order for the SCC to be transmitted throughout the system (the daisy-chained Slave PCI-1000 units will auto-recognize the Slave mode). To do this, use a single-pin LEMO cable (part number CBL-1P1) to connect SCC OUT of the Master PCI unit to SCC IN of the first Slave unit. These connectors are located on the back of the PCI unit. Continue in this manner until all PCI units are daisy-chained together. This operation may be performed on any combination of PCI models (the current software supports up to five PCI-1000 units).

## 2.4 Software Installation and Configuration

The PCS102 Control Software is designed for IBM-PC compatible computers running Microsoft Windows XP, 2k, 9x, or NT. The SQUID Amplifier Control Module and the PCI Module (for the PCI-1000 Interface unit) are supplied as an integrated installation package (STAR Cryoelectronics Model Number SW-SA). The present version of the software does not include a data acquisition module.

The PCS102 Control Software was developed using National Instruments' LabWindows/CVI. Running this software requires the CVI Run-Time Engine, which is included in your software package and installed automatically.

### 2.4.1 First-Time Installation Procedure

- 1. The installation is performed while running Windows. For best results, quit all other applications before installing the PCS102 software.

- 2. Insert the installation CD into a CD drive of your computer. Double-click on the "My Computer" icon, and then click on the "Compact Disc" icon. The installation CD contains a folder named "PCS102\_Kit". Open this folder.

- 3. Double-click on the icon "Setup.exe". The installation software will launch and display the message "Welcome to the PCS102 Installation Wizard". Follow the instructions of the installation Wizard. The default installation directory for the PCS102 software is C:\Program Files\PCS102. A different folder can be selected during the installation process if necessary.

- 4. After all installation steps have been completed, the message "PCS102 has been successfully installed" will be displayed. To run the program, go to the "Start" menu and select Programs>pcSQUID>PCS102. Alternately, a shortcut may be created and placed on your desktop by right-clicking on a free area on your desktop and selecting New>Shortcut. On the Create Shortcut panel, click on "Browse…" and select the file C:\Program Files\pcSQUID\PCS102.exe. Click on Next> to continue, and enter a name for the shortcut (*e.g.*, PCS102). Click on Finish to create the shortcut.

## 2.4.2 Procedure to Replace an Existing Software Version

Run the utility program "setup.exe" which is a part of the new installation package. The existing version of the software will be uninstalled automatically. Then follow the steps in Section 2.4.1.

## 2.4.3 Software Configuration Procedure

- 1. Turn the PC Interface ON, and launch the PCS102 software by clicking on Start>Programs>pcSQUID>PCS102 (or by clicking on the desktop shortcut created as described in Section 2.4.1).

- 2. After the splash panel is displayed, the main panel with control, tuning, and configuration sections will appear. From the main menu, select CONF, and then "System" (or use the hot-key Y). A system configuration panel will appear.

- 3. Use the "Number of Channels" control to set the number of channels equal to the number of connected PFL-102 units. Set the "PCI Units" control to either PCI-100 or the appropriate number of PCI-1000 units.

- 4. Use the "Port" control to select the port you wish to use. The default port is COM1 (for applications requiring higher-speed communications with the PFL-102, the parallel port interface should be used). The "Status" indicator shows the state of the selected port ("Enabled" or "Disabled"). The "Transmission" indicator reports whether data have been successfully written to this port ("Success" or "Failure"). Make sure that the port connected to the PC Interface is enabled. If the port is disabled, no data will be sent. If the port is enabled, but an error occurs during data transfer, a popup window with the message "Data transmission was unsuccessful" will appear. This may happen, for example, if the appropriate port is not connected to the PC Interface. Check if the connection is correct, and

click the "Try again" button. If this does not help, click the "Change port" button and select a different port. Then use the REFRESH button on the Main panel to resend all data.

- 5. If the data transfer is successful, the DATA LED on the side of the PFL-102 unit, corresponding to the selected channel, should turn green. A further test is to send a HEAT command: the HEATER LED should turn orange and remain lit during the heating time. If this does not happen, check the hardware address switch settings inside the PFL (see detailed instructions in Section 5.2). The binary address (with ON corresponding to binary 0, and OFF to binary 1) of each unit should be equal to the channel number.

- 6. Multiple initialization files can be used to store different configuration settings. When the PCS102 Control Software is run for the first time, the initialization file is file1.ini. You can use the "File" control on the system configuration panel to select a different file, and click "Restart" to restart the program with this file. If it does not exist, it will be created with the default settings. For greater reliability, the file names are predefined (file1.ini, file2.ini, ...), but each file can be assigned a unique label. A sample initialization file with default settings is given in Section 2.4.4. Up to nine different initialization files may be defined. To define a new label for an initialization file, enter the desired text into the field of the "Label" control, and click the "Label On" button to assign it to the chosen file. The initialization file in use is updated whenever the program is shut down. When it is started the next time, the updated initialization file is used to restore the last configuration. Different users are recommended to store their settings in different files, and switch from one configuration to another using the "Restart" command. If the same file will be used every time, there is no need to modify the "File" control.

- 7. You can right-click on any control to view its description and hot key assignment on the information bar at the bottom of each panel. Any command is executed immediately when the corresponding control is used. If any PFL was temporarily turned off or disconnected, use the REFRESH button to restore all settings.

| 🍻 System Configu                                              | ration            | - I X                   |  |

|---------------------------------------------------------------|-------------------|-------------------------|--|

| Number of Cł                                                  | annels)           | PCI Units               |  |

| Port                                                          | Status<br>Enabled | Transmission<br>Success |  |

| File<br>File 1                                                |                   | Label                   |  |

|                                                               | Restart           | Label On OK             |  |

| Number of channels. Keys: Ctrl+N to activate; Up,Dn to modify |                   |                         |  |

Figure 2-1 System Configuration panel.

#### 2.4.4 Initialization Files and Default Settings

A sample initialization file with default settings is shown below. If hardware updates or modifications are made to the PFL-102 or PCI-1000, the labels displayed by the software may be changed by editing the appropriate hardware labels in the initialization file. For example, if the maximum array bias range is changed as discussed in Section 5.6, the ABIASMAX label in the hardware section of the initialization file should be edited to agree with the new maximum array bias range. The hardware labels associated with specific software controls are discussed in more detail in Section 4.2 (PFL-102 controls) and Section 4.3 (PCI-1000 controls).

Note that if hardware modifications are made to a specific PFL-102, a corresponding initialization file for the modified PFL should be created and used whenever operating the modified PFL; otherwise, the parameters displayed by the control software will not match the actual parameters of the PFL.

#### Default settings for file1.ini:

[CUSTOM] SETFILE=1 LABEL1= LABEL2= LABEL3= LABEL4= LABEL5= LABEL6= LABEL7= LABEL8= LABEL9= ----= [HARDWARE] SBIASMAX=2.000000 SFLUXMAX=100.00000 ABIASMAX=100.000000 AFLUXMAX=200.00000 OFFSETMAX=9.800000 PCIAMPMAX=5.000000 TIMESHIFT=0.000000 RESLOW=1 kOhm RESMED=10 kOhm RESHIGH=100 kOhm CAPLOW=1.5 nF CAPMED=15 nF CAPHIGH=150 nF FILTERA=LP 3 kHz FILTERB=LP 6 kHz FILTERC=LP 15 kHz FILTERD=LP 30 kHz ----= [SYSTEM] SELCH=0 NCHANNELS=1 NPCIUNITS=1 GROUPSIZE=1 PRECISION=1 PORT=4 ----=

[SQ\_0] DACSSTATE=1 DACASTATE=1 SBIAS=0 SFLUX=0 ABIAS=0 AFLUX=0 OFFSET=0 RESET=0 SMODE=0 AMODE = 0RANGE=1 FBRES=0 INTCAP=2 TESTSIG=2 TESTINP=4 ONTIME=2 COOLTIME=5 ----= [PCI\_0] ADDRESS=255 INDEX=0 TESTSRC=0 TESTFREQ=100 TESTAMP=1024 FRONTOUTMODE=0 FRONTOUTCHAN=0 FSELCH=0 STEPSIZE=20 TESTOUTEN 0=1 FILTER\_0=0  $MPLEX_0=0$ TESTOUTEN\_1=1 FILTER\_1=0 MPLEX\_1=0 TESTOUTEN\_2=1 FILTER\_2=0 MPLEX\_2=0 TESTOUTEN 3=1 FILTER\_3=0  $MPLEX_3=0$ TESTOUTEN\_4=1 FILTER\_4=0 MPLEX\_4=0 TESTOUTEN\_5=1 FILTER\_5=0  $MPLEX_5=0$ TESTOUTEN\_6=1 FILTER\_6=0  $MPLEX_6=0$ TESTOUTEN\_7=1 FILTER\_7=0 MPLEX\_7=0 ----=

## **3** Operation

## 3.1 Two-Stage SQUID Amplifier Overview

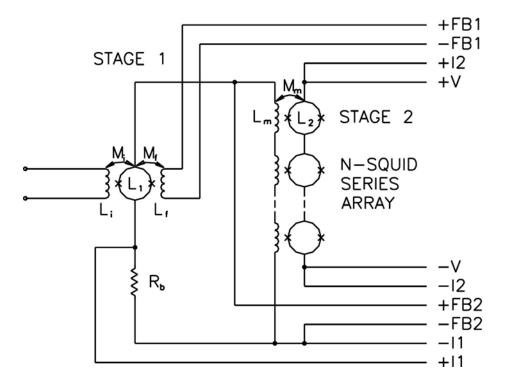

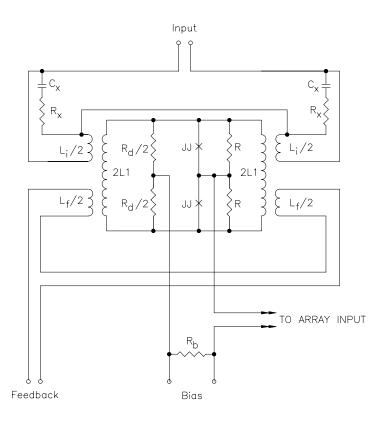

The Programmable Feedback Loop Model PFL-102 is designed to operate two-stage SQUID amplifiers, which are available separately from STAR Cryoelectronics. Originally developed by Martinis and Welty,<sup>1</sup> the two-stage amplifier design is shown schematically in Figure 3-1. The low-noise SQUID in the input stage is voltage-biased using resistor  $R_b$  and SQUID bias current I1. The input SQUID is connected in series with the modulation coils of a series array of N identical, non-hysteretic SQUIDs in the output stage. The total inductance of the array modulation coils is  $NL_m$ .

The output SQUID array is current biased using bias current I2. A changing signal coupled to the input SQUID causes the current through the input SQUID to change, which in turn coherently modulates the series SQUID array in the output stage. A substantial output voltage swing can be realized in this way with a reasonable number of series-connected SQUIDs in the second stage.

The second stage is directly coupled to a low-noise preamplifier in the room temperature feedback electronics. The second stage is designed with sufficient gain such that the output noise is dominated by the amplified noise of the input SQUID and exceeds the noise of the room-temperature preamplifier. Thus, flux modulation and impedance matching circuits are not required, and the system bandwidth and slew rate can therefore be very high.

STAR Cryoelectronics offers integrated two-stage SQUID amplifiers (SA1*xx*/SA6*xx* series) as well as series SQUID arrays (AR*xx* series). The SQUID amplifiers are available mounted in a miniature package with screw terminals and solder pads for all electrical connections to the amplifier. The miniature package includes an efficient heater resistor to de-flux the SQUID amplifier if necessary. The SQUID amplifier package is compatible with operation in liquid cryogen or vacuum, and is available mounted in a niobium shield assembly with connector interface, or in a small, connectorless niobium shield assembly for applications requiring a more compact sensor size. Optional mating cryocables are available.

To operate the SQUID amplifier, one first tunes the output array stage to obtain the largest output signal  $\Delta V$ . This is done by injecting a test signal into the modulation coils of the array and adjusting the array bias current. The optimal working point for locked-loop operation is then set using a voltage offset such that the steepest part of the flux-to-voltage transfer function is at zero Volts. The array may then be locked at this working point.

To tune the input SQUID stage, the locked array is used as a preamplifier to record the SQUID output. The voltage bias across the input SQUID is set by adjusting the SQUID bias current. With the test signal now coupled to the input SQUID and the array locked, the SQUID bias is adjusted to maximize the SQUID output signal  $\Delta I$ . When the SQUID is locked, the array is automatically opened and now operates as a small signal amplifier. In order to enhance linearity, the STAR Cryoelectronics amplifiers are designed such that the maximum current swing of the

<sup>&</sup>lt;sup>1</sup> Welty, R.P. and Martinis, J.M. (1993) Two-stage integrated SQUID amplifier with series array output, *IEEE Trans. Appl. Superconductivity* **3**, 2605-2608.

input SQUID is less than the current required to produce a flux change of one flux quantum in the output array.

More detailed information about tuning and operating SQUID amplifiers using the Model PFL-102 Programmable Feedback Loop is discussed in the following sections.

Figure 3-1 Schematic diagram of a typical two-stage SQUID amplifier.

## **3.2 Tuning the Output Array**

A test signal is used to tune the output array and input SQUID. The array usually is tuned first, then the locked array is used to tune the input SQUID. The test signal is coupled to the array or input SQUID via the TEST INPUT BNC connector on the front panel of the PCI unit. An external signal generator is required if you are using a PCI-100; if you are using a PCI-1000, the internal test signal generator may be used instead of an external signal source.

*Note*: A high-frequency test signal may be coupled directly to the SQUID amplifier via the TEST IN connector on the PFL-102. A 1-pin LEMO-to-BNC adapter cable is needed in this case.

## 3.2.1 Tuning the Output Array using a Time-Base Display

- 1. Connect an oscilloscope to the WB OUT of the PFL-102 unit (or to the WIDEBAND output BNC on the front panel of the PC Interface if the PFL-102 has been configured to enable this option see Section 5.3). If a PCI-100 interface is used, connect a signal generator to the TEST INPUT BNC on the front panel of the PC Interface. Connect the synchronization output of the generator to the EXT TRIG input of the oscilloscope. If you are using the internal test signal generator of the PCI-1000, the synchronization signal should be taken from the SYNC OUT BNC on the rear panel of the PCI-1000.

- 2. Start the PCS102 Control Software. Set the TEST SIGNAL control to "On" or "Auto" (if the "Auto" mode is used, the test signal is On in the TUNE mode, but switched Off in the LOCK mode). Set the TEST INPUT control to "Array Flux". Configure the test signal generator for a triangle waveform with a frequency around 100 Hz to 200 Hz. An external test signal is required if you are using a PCI-100; with the PCI-1000, an external or the internal test signal generator may be used. The proper test signal amplitude will depend on the design of the series SQUID array used. For STAR Cryoelectronics' SA1xx/SA6xx amplifiers and ARxx arrays, set the test signal amplitude to 0.4 V. This value of the test signal amplitude will approximately correspond to one flux quantum.

- 3. To simplify array bias adjustment, the array output signal may be AC coupled to the oscilloscope. Then, increase the array bias current using the A-BIAS control to maximize the peak-to-peak magnitude of the output voltage signal. For STAR Cryoelectronics' SA1*xx*/SA6*xx* amplifiers and AR*xx* arrays, the optimum bias current is around 40 to 60  $\mu$ A, and the maximum output signal should be 3 to 5 V<sub>pp</sub> depending on the array type. If the signal magnitude is much smaller, use the HEAT command to warm the amplifier (or array) to release trapped flux in the array. Typically, a heat time of 0.2 seconds and a cool time of 4 seconds is sufficient. In some cases, it may be necessary to repeat the heat cycle several times.

- 4. Once the array bias has been adjusted to maximize the array output, switch the oscilloscope back to DC coupling and adjust the OFFSET control until the steepest slope of the output signal is at zero Volts. Note that it may be necessary to adjust the A-FLUX control to view the steepest slope.

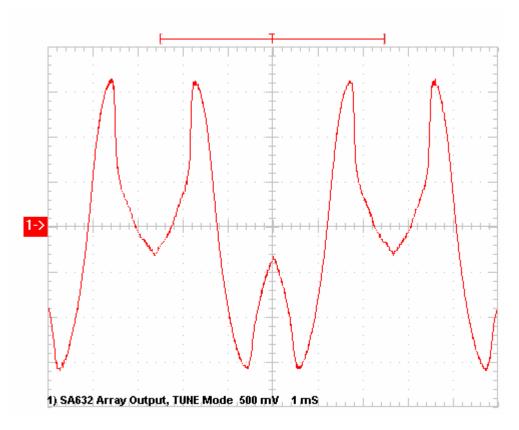

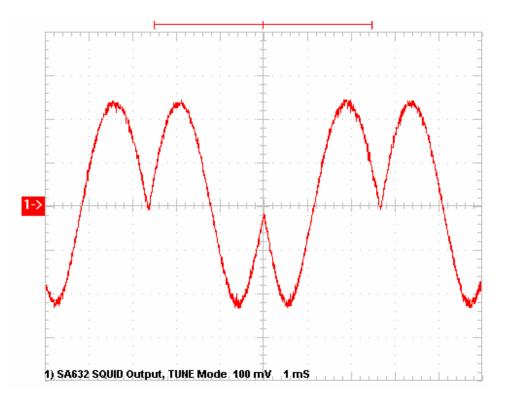

A typical time trace of the voltage output of a STAR Cryoelectronics SA632 SQUID amplifier in TUNE mode is shown in Figure 3-2. A 190 Hz triangular test signal with an amplitude of 0.389 V is coupled to the array using the "Array Flux" option for the test signal input. The amplitude is adjusted so that sharp peaks and dips, pointing towards the mean value of the output and corresponding to the positive and negative peaks of the test signal, are at the same horizontal level. In this case, the peak-to-peak magnitude of the test signal, 0.778 V<sub>p-p</sub>, corresponds to one flux quantum. The PFL output voltage swing is  $3.2 V_{p-p}$ . The voltage gain of the PFL-102 is 5040, so the actual array voltage swing is 0.635 mV<sub>p-p</sub>. For the SA632 amplifier, the array consists of 32 SQUIDs connected in series; thus the average voltage swing per SQUID is about 20  $\mu$ V<sub>p-p</sub> in this case.

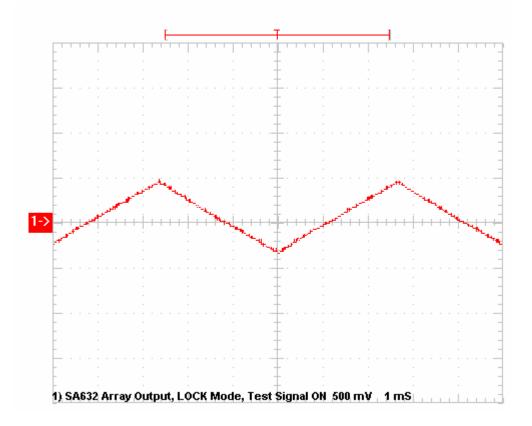

- 5. After tuning the array as described above, click on the A-LOCK command button to operate the array in the LOCK mode. Alternately, you may click on the State indicator for the array. If the TEST SIGNAL control is "On", the array output should follow the applied test signal. If this control is set to "Auto", the output should be a horizontal line.

- 6. The SENSITIVITY, FEEDBACK, and INTEGRATOR controls can be used to select the feedback loop parameters. When the SENSITIVITY range is changed, the feedback resistor and integrator capacitor are changed together in order to preserve bandwidth. In order to manually select the feedback resistor and integrator capacitor values, set the SENSITIVITY control to "Select R&C". If the output voltage is off scale, click on RESET to reset the feedback loop. The A-FLUX control may then be used to zero the array output.

Figure 3-2 Time trace of the PFL-102 output with the array in TUNE mode. A test signal with peak-to-peak magnitude corresponding to 1  $\Phi_0$  is used to modulate the array.

7. To calibrate the locked array, use the A-FLUX control to shift the output sufficiently away from zero such that clicking on RESET causes the output to jump by exactly one flux quantum. This can be done using a multimeter to record the PFL output voltage before and after resetting the feedback loop; the difference of these two voltages then gives the calibration factor in V/ $\Phi_0$  (assuming the flux jump corresponds to 1  $\Phi_0$ ). Note that the ARRAY FLUX must be incrementally adjusted until clicking on RESET causes the output to jump; otherwise it is possible to shift the output voltage so far that the jump following a RESET corresponds to multiple flux quanta. Note also that, if the sensitivity range is changed or another feedback resistor is selected, the array must be re-calibrated for locked-loop operation using the new configuration.

If the output voltage is sufficiently large, but the RESET command does not cause a jump, the preamplifier offset may not be adjusted properly. Switch back to the TUNE mode and adjust the OFFSET control as described in the previous section. *Do not change the preamplifier offset in the LOCK mode, because this will change the working point for closed-loop operation.*

A typical output of the PFL-102 unit with the array in the LOCK mode with the SENSITIVITY range set to "High" is shown in . The TEST SIGNAL is set to "On", and the output voltage tracks the test signal. In this case, the feedback resistor is  $100 \text{ k}\Omega$  and the integrator capacitor is 1.5 nF.

Figure 3-3 Output of the PFL-102 in LOCK mode. The output voltage tracks the applied test signal, which is used to modulate the array.

## 3.2.2 Viewing the DC Characteristics of the Array: V- $\Phi$

To view the dc characteristics of the array, an external generator and oscilloscope with X-Y mode are required.

*Note:* If you are using a PCI-1000, you may use the internal test signal generator instead of an external generator to view the dc characteristics. Open the PCI panel for the channel you are using (the PCI panel may be brought up by selecting MODULE>Show PCI on the Main panel) and configure the Multiplexer control for "Test Signal" (see Section 4.3.3). In this configuration, the internal test signal is available at the FILTERED BNC on the front panel of the PC Interface. You may use this signal source instead of the external signal generator in the discussion below.

1. To view the V- $\Phi$  characteristics, connect the WB OUT terminal of the PFL-102 (or the WIDEBAND output of the PC Interface if the PFL-102 has been configured to enable this option - see Section 5.3) to the vertical input of the oscilloscope. Using a tee-connector, connect the signal generator output to the horizontal input of the oscilloscope and to the TEST SIGNAL input on the PC Interface. Configure the signal generator for a 100 Hz triangle wave with an amplitude of around 1 Volt. For the array flux test signal input, 1 V corresponds to a current of 10  $\mu$ A through the array modulation coil.

*Note*: The outputs at the WIDEBAND and FILTERED BNC connectors on the front panel of the PCI-100 and PCI-1000 are inverted; the output at the WB OUT 1-pin LEMO connector on the PFL-102 is *not* inverted.

2. Set the TEST SIGNAL control to "Auto" or "On", and the TEST INPUT control to "Array Flux". Adjust the A-BIAS control to maximize the output voltage. Note that it may be necessary to adjust the OFFSET and A-FLUX controls to center the trace on the display of the oscilloscope. If the vertical voltage swing of the array V- $\Phi$  characteristic is much less than a few Volts, the sensor should be heated to release flux trapped in the array.

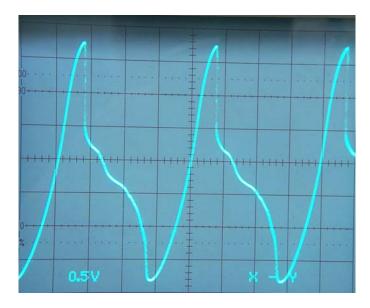

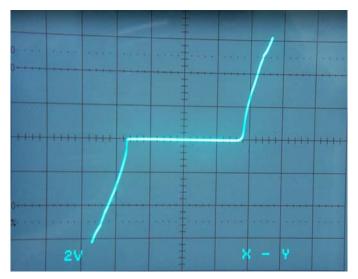

The V- $\Phi$  characteristic of the output array stage of a SA632 SQUID amplifier is shown in Figure 3-4. Since the voltage gain of the PFL-102 is 5040, the vertical scale is 0.198 mV/div. The horizontal scale is 2  $\mu$ A/div. As can be seen in Figure 3-4, the current required to produce a change of 1  $\Phi_0$  in the array is roughly 7.8  $\mu$ A (use the procedure outlined in Section 3.2 to calibrate the PFL for a given feedback resistor to obtain a more exact determination of the feedback current required per flux quantum). Using the scale factors for X and Y, the flux-to-voltage transfer function  $\partial V/\partial \Phi$  of the array may then be measured at any point by expanding the scales on the oscilloscope.

*Note*: Although the array V- $\Phi$  characteristic exhibits structures on the negative slope indicative of resonances in the array dynamics, the positive slope is smooth and free of such structures. The feedback connections in the PFL-102 have been configured such that the array will lock on the smooth, positive slope (using SA1*xx*/SA6*xx* amplifiers). In this case, amplifier noise and bandwidth will be optimal. Locking on the negative slope will result in increased noise and reduced bandwidth. If other amplifiers or arrays are used, it may be necessary to reverse the polarity of the feedback connections to the amplifier or array in order to lock on the slope with largest flux to voltage transfer function.

Figure 3-4 Output V- $\Phi$  characteristic of the array in X-Y mode. The output voltage of the PFL-102 is plotted versus the test signal voltage. Since the PFL voltage gain is 5040, the vertical scale is 0.198 mV/div. The horizontal scale is 2  $\mu$ A/div.

- 3.2.3 Viewing the DC Characteristics of the Array: V-I

- 1. To view the voltage-current characteristic of the array, configure the external signal generator and oscilloscope as described in Section 3.2.2 above. Set the A-BIAS control to zero and the TEST INPUT control to "Array Bias".

- 2. Increase the amplitude of the test signal to sweep out the *V*-*I* characteristic. Note that it may be necessary to adjust the preamplifier OFFSET so there is no voltage offset when the array is in the zero voltage state. For the array bias test signal input, 1 V corresponds to a current of 10  $\mu$ A through the array. The *V*-*I* characteristic may be modulated by varying the array flux using the A-FLUX control.

*Note*: The outputs at the WIDEBAND and FILTERED BNC connectors on the front panel of the PCI-100 and PCI-1000 are inverted; the output at the WB OUT 1-pin LEMO connector on the PFL-102 is *not* inverted.

The *V-I* characteristic of the output array stage of a SA632 SQUID amplifier is shown in Figure 3-5. The A-FLUX setting has been adjusted to maximize the critical current along the positive (right) side of the trace.

The dynamic resistance of the array at the intended operating point may be measured in the *V-I* mode. Tune the array by adjusting the array bias current and offset flux as described in Section 3.2.1 for the desired working point, then reduce the amplitude of the test signal to around 0.005  $V_{pp}$  and set the TEST INPUT to "Array Bias" (to select the *V-I* mode). Do not change the bias or flux offset settings. The trace on the oscilloscope display may now be amplified to measure the dynamic resistance at the chosen working point.

Figure 3-5 Voltage-Current characteristic of the output array of a SA632 amplifier. The output voltage of the PFL-102 is plotted versus the test signal voltage, which is used to produce the bias current. The PFL voltage gain is 5040, so the vertical scale is 0.397 mV/div. The horizontal scale is  $20 \,\mu$ A/div.

#### 3.2.4 Array Noise Measurements

- 1. To measure the array noise, connect the WIDEBAND output at the 1-pin LEMO connector on the PFL-102 to a spectrum analyzer. The rms flux noise may be calculated by dividing the measured rms voltage noise by the calibration factor in  $V/\Phi_0$  determined in Section 3.2.1. Alternately, the noise may be measured with the array unlocked. In this case, the rms voltage noise should be divided by the flux-to-voltage transfer coefficient measured at the working point of interest. Both measurements should be comparable.

- 2. Using exponential averaging with a small number of iterations (*e.g.*, 32), it is possible to fine tune the array bias and preamplifier offset settings to minimize the noise. Make a note of these settings for future reference.

*Note*: If the input SQUID is in the zero voltage state (e.g., the input SQUID bias setting is set to zero), the rms voltage (or flux) noise of the array will be dominated by the Johnson noise owing to the voltage bias resistor  $R_b$ . A measurement of the noise in this case allows the user to determine the precise value of  $R_b$  (see Section 3.2.5 below). Biasing the input SQUID well above the critical current of the input SQUID will reduce this noise contribution, but one will always measure some non-negligible noise contribution from the dynamic resistance of the input SQUID.

#### 3.2.5 Bias Resistor Determination

The resistance of the bias resistor used to voltage bias the input SQUID may be determined by measuring the voltage noise of the array with the input SQUID in the zero voltage state (e.g., with the SQUID bias setting set to zero). The rms voltage noise is given by  $V_n = \sqrt{4k_BT/R_b}$ , where  $k_B$  is Boltzmann's constant and *T* is the temperature. Using this expression, one may determine  $R_b$  (typically 100 m $\Omega$ ), which is needed to determine the actual current through the SQUID.

*Note*: Using STAR Cryoelectronics SA1*xx* or SA6*xx* series two-stage amplifiers, one must also take into account the damping resistors  $R_d/2$  in the input SQUID circuit (see Figure 3-6 and SQUID Amplifier SA1*xx*/SA6*xx* Data Sheet). In this case,  $R_b$  in the expression above for the voltage noise should be replaced by  $(R_b + R_d/4)$ . The resistance  $R_d/4$  can be determined from the input SQUID *V*-*I* characteristic.

Figure 3-6 Schematic diagram of the input SQUID stage of STAR Cryoelectronics' SA1*xx*/SA6*xx* series SQUID amplifiers.

## 3.3 Tuning the Input SQUID

To tune the input SQUID, the output array should first be locked. The array is then used as a preamplifier in order to view the SQUID *I*- $\Phi$  and *V*-*I* characteristics. Tune and lock the array as described in Section 3.2 above before proceeding. Once the array is locked, do not change the array bias or preamplifier offset settings.

## 3.3.1 Tuning the Input SQUID using a Time-Base Display

- 1. Tune and lock the array as described in Section 3.2 above. When tuning the array, set the input SQUID bias to a high enough value (*e.g.*, 1 mA) such that the current through the input SQUID exceeds the critical current of the input SQUID.

- 2. Configure the test signal generator for a 100 Hz to 200 Hz triangle wave with an amplitude of around 1  $V_{pp}$ , and set the TEST INPUT control to "SQUID Flux". If no trace is visible on the oscilloscope display, click on the RESET command button to reset the locked array. Adjust the S-BIAS control (*e.g.*, decrease the input SQUID bias from the value used to tune the array) to increase the current swing of the SQUID *I*- $\Phi$  characteristic. If the input SQUID bias current is reduced to far, the array will eventually loose lock; if this happens, increase the input SQUID bias slightly and click on RESET to reset the feedback loop. If the *I*- $\Phi$  characteristic moves out of range as the input SQUID bias is adjusted, reset the locked array, or use the A-FLUX control to re-position the characteristic near the middle of the oscilloscope display.

- 3. Adjust the S-BIAS to obtain a swing of around 4 to  $6 \mu A_{p-p}$ . Then adjust the A-FLUX control to position the *I*- $\Phi$  characteristic such that the steepest point on the positive-going slope intersects the zero Volt reference line on the oscilloscope display. The S-FLUX control may be used to shift the characteristic horizontally.

A typical time trace of the input SQUID *I*- $\Phi$  characteristic of a STAR Cryoelectronics SA632 SQUID amplifier with the input SQUID in TUNE mode is shown in Figure 3-7. A 190 Hz triangular test signal with an amplitude of 0.274 V is coupled to the input SQUID by selecting the "SQUID Flux" option for the test signal input. The amplitude is adjusted as before such that the sharp peaks and dips are at the same level. Then, the peak-to-peak magnitude of the test signal, 0.549 V<sub>p-p</sub>, corresponds to one flux quantum. For this trace, the output array is locked using the "High" settings (100 k $\Omega$ , 1.5 nF) 1 V output from the array corresponds to 10  $\mu$ A through the SQUID (and array input coil). The output voltage swing is 0.48 V<sub>p-p</sub>, corresponding to an input SQUID current swing of 4.8  $\mu$ A<sub>p-p</sub>.

Figure 3-7 Time trace of the PFL-102 output with the array locked and input SQUID in TUNE mode. A test signal with peak-to-peak magnitude corresponding to 1  $\Phi_0$  is used to modulate the input SQUID.

- 4. After tuning the SQUID as described above, click on the S-LOCK command button to lock the SQUID. Alternately, you may click on the State indicator for the SQUID. The output array is automatically put into the TUNE mode, and acts as a preamplifier for the SQUID signal. If the TEST SIGNAL control is "On", the output should follow the applied test signal. If this control is set to "Auto", the output should be a horizontal line.

- 5. The SENSITIVITY, FEEDBACK, and INTEGRATOR controls can be used to select the feedback loop parameters. When the SENSITIVITY range is changed, the feedback resistor and integrator capacitor are changed together in order to preserve bandwidth. In order to manually select the feedback resistor and integrator capacitor values, set the SENSITIVITY control to "Select R&C" mode. If the output voltage is off scale, click on the RESET button to reset the feedback loop. The S-FLUX control may then be used to zero the output.

- 6. To calibrate the amplifier for locked-loop operation, use the S-FLUX control to shift the output sufficiently away from zero such that a RESET command causes a jump by exactly one flux quantum. As discussed in Section 3.2.1, use a multimeter to record the PFL output voltage before and after resetting the feedback loop; the difference of these two voltages then gives the calibration factor in V/ $\Phi_0$  (assuming the flux jump corresponds to 1  $\Phi_0$ ). If the sensitivity range is changed or another feedback resistor is selected, the SQUID must be recalibrated for locked-loop operation using the new configuration.

Note: Do not change the preamplifier offset or array bias settings while tuning the SQUID. Doing so will change the optimal working point for the array.

## 3.3.2 Viewing the DC Characteristics of the Input SQUID: $I-\Phi$

To view the dc characteristics of the input SQUID, an external test signal generator and oscilloscope with X-Y mode are required. The locked array is used as a preamplifier in order to view the SQUID *I*- $\Phi$  and *V-I* characteristics. Tune and lock the array as described in Section 3.2 above before proceeding. Once the array is locked, do not change the array bias or preamplifier offset settings.

*Note:* If you are using a PCI-1000, you may use the internal test signal generator instead of an external generator to view the dc characteristics. Open the PCI panel for the channel you are using (the PCI panel may be brought up by selecting MODULE>Show PCI on the Main panel) and configure the Multiplexer control for "Test Signal" (see Section 4.3.3). In this configuration, the internal test signal is available at the FILTERED BNC on the front panel of the PC Interface. You may use this signal source instead of the external signal generator in the discussion below.

- 1. To view the *I*- $\Phi$  characteristics of the input SQUID, connect the WB OUT terminal of the PFL-102 (or the WIDEBAND output of the PC Interface if the PFL-102 has been configured to enable this option see Section 5.3) to the vertical input of the oscilloscope. Using a tee-connector, connect the signal generator output to the horizontal input of the oscilloscope and to the TEST SIGNAL input on the PC Interface. Configure the signal generator for a 100 Hz triangle wave with an amplitude of around 1 Volt. For the SQUID flux test signal input, 1 V corresponds to a current of 10  $\mu$ A through the SQUID modulation coil.

- 2. Set the TEST SIGNAL control to "Auto" or "On", and the TEST INPUT control to "SQUID Flux". Adjust the S-BIAS current to optimize the current swing of the SQUID *I*- $\Phi$  characteristic. If the *I*- $\Phi$  characteristic moves out of range as the SQUID bias is adjusted, click on RESET to reset the locked array, or use the A-FLUX control to re-position the characteristic near the middle of the oscilloscope display.

The vertical scale for the *I*- $\Phi$  characteristic is determined by the SENSITIVITY range (or feedback resistor) selected for the locked array. For example, using the "high" sensitivity range (100 k $\Omega$ ), the vertical scale is 1  $\mu$ A/div. For the horizontal scale, 1 V form the test signal corresponds to 10  $\mu$ A coupled to the input SQUID feedback coil. Knowing the scale factors for X and Y, the flux-to-current transfer function  $\partial I/\partial \Phi$  of the input SQUID may be measured by expanding the scales on the oscilloscope.

## 3.3.3 Viewing the DC Characteristics of the Input SQUID: V-I

- 1. To view the current-voltage characteristic of the input SQUID, set the S-BIAS control to zero, and the TEST INPUT control to "SQUID Bias". For the SQUID bias test signal input, 1 V corresponds to a current of 200  $\mu$ A through the bias resistor  $R_b$  (see Figure 3-1). To determine the actual current through the input SQUID, it is necessary to know the exact value of  $R_b$ . This may be done using the procedure discussed in Section 3.2.5.

- 2. Increase the amplitude of the test signal to sweep out the input SQUID *V-I* characteristic. It may be necessary to reset the locked array or increase the SQUID bias current in order to trace out a larger portion of the SQUID *V-I* characteristic. It may be difficult to keep the array locked as the input SQUID is biased close to the zero voltage state if  $\partial I/\partial \Phi$  gets too

high. The *V-I* characteristic may be modulated by varying the SQUID offset flux using the S-FLUX control.

3. The dynamic resistance of the SQUID at the intended operating point may be measured in the *V-I* mode. Adjust the S-BIAS and S-FLUX controls for the desired working point as described in Section 3.2, then reduce the amplitude of the test signal to around 0.005  $V_{pp}$  and set the TEST INPUT to "SQUID Bias" (to select the *V-I* mode). Do not change the bias or flux offset settings. The trace on the oscilloscope display may now be amplified to measure the dynamic resistance at the chosen working point.

# 4 PCS102 Control Software

This section describes the detailed operation of the P102 Control Software for Microsoft Windows<sup>TM</sup> XP, 2k, 9x, and NT.

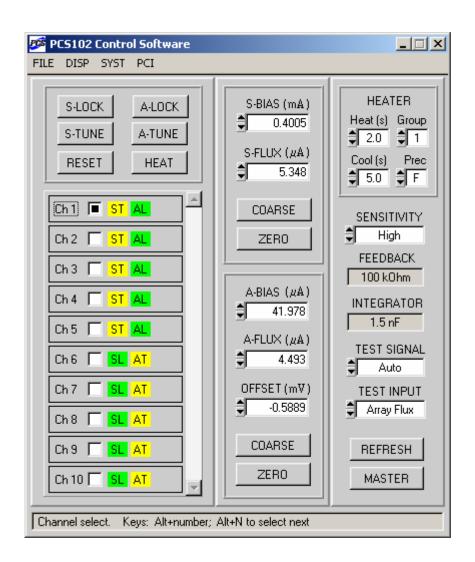

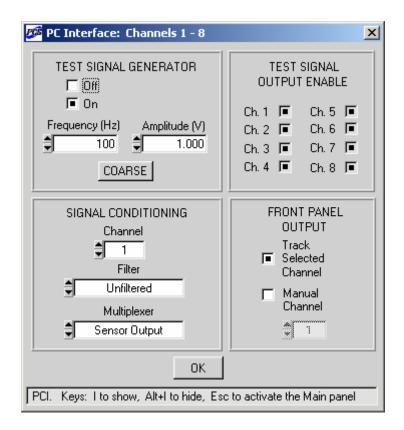

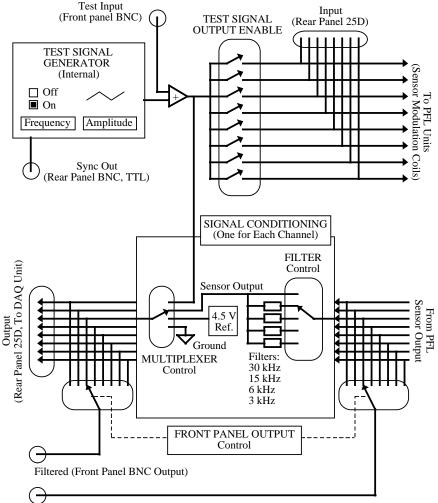

The user interface of the PCS102 software consists of three different panels. The Main panel allows one to tune, configure and control each channel. The System Configuration panel is used to configure the hardware parameters and settings files. The PCI panel is used to configure the PC Interface (PCI-1000 only), such as the internal test signal generator or signal conditioning. The current software supports up to five PCI-1000 units connected in a daisy-chain fashion. Each PCI-1000 unit in your system is controlled using an individual PCI panel, which is labeled according to the channels connected to that PCI-1000 unit, such as channels 1-8, channels 9-16, etc. The single-channel PCI-100 interface has no configurable or remotely controllable hardware, and therefore there is no PCI panel for the PCI-100.

## 4.1 Operating the Software: A Brief Look

When the software is launched for the first time, the default settings are used. Your first step should be to configure the software for the hardware you have installed. This is done using the System Configuration panel (see Figure), which is brought up by selecting the CONF>System menu. Please refer to Section 2.4 for detailed instructions on how to configure the system. Note that the operation of the System Configuration panel is fully interactive, and all settings take effect immediately. The only exception is the settings file selection: the "Restart" button should be used to restart the program using a different settings file.

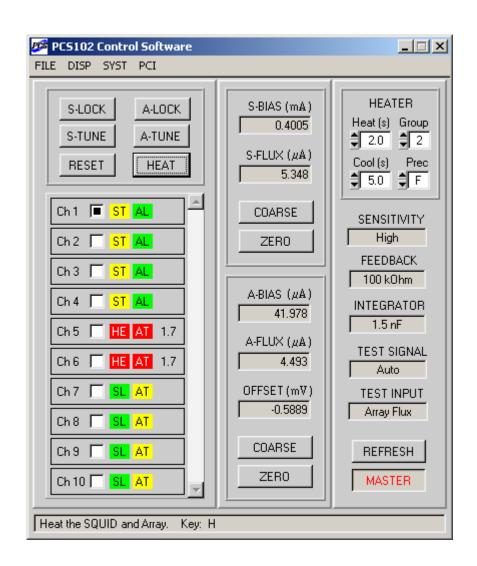

The Main panel is shown in Figure 4-1. It consists of three vertical sub-panels. The left subpanel is the Control section, which contains command buttons to select the operating mode. It also includes a display showing the state of every installed channel.

The middle sub-panel is the Tune section. It includes separate numeric controls to tune the SQUID and the array independently for the selected channel.

The right sub-panel is the Configuration section. This section is used to configure the feedback loop parameters and test signal mode and coupling for the selected channel. It also contains the heater controls.

In addition to these three major sections, the Main panel has an information bar at the bottom of the panel. Every time a control is operated, activated, or right-clicked, a description of this control, together with its hot key assignment, appears at the bottom of the Main panel. The System Configuration and PCI panels are also equipped with information bars, which display information about their controls.

Each channel is represented in the Control section by its own small panel with four control indicators, which are used to display information about each channel, change its state, and select that channel for subsequent action. To select a channel, simply use the mouse to click on the Select box located on the right of the channel number. Only one channel may be selected at a time. Detailed information about the selected channel is displayed in the Tune and Configuration sections of the Main panel. When a different channel is selected, the settings for that channel are then displayed. In this way, the settings for each channel may be adjusted independently.

Next to the Select box, there are two colored State indicators. The left one corresponds to the input SQUID, the right one - to the output array. The State indicators are yellow in the TUNE mode, and green in the LOCK mode. One can switch between the two modes simply clicking on a State indicator. The corresponding channel then automatically becomes selected. Note that the input SQUID and the output array cannot be locked simultaneously, and, therefore, no more than one State indicator for any channel can be green at a time.

Figure 4-1 The Main panel for 10-channel operation. Channel 1 is the selected channel. All settings displayed on the right correspond to this channel. The first five channels have the input SQUIDs in the TUNE mode ("ST"), and the output arrays in the LOCK mode ("AL"). For the next five channels, the SQUIDs are locked ("SL"), with the arrays in the TUNE mode ("AT").

The State indicators turn red during heating and turn blue during subsequent cooling. The Count indicator on the right of them, which is visible only during a heat cycle, exhibits the amount of time, in seconds, left for heating or cooling. Note that, during a heat cycle, all controls, except for the heater controls and State indicators, are disabled and cannot be changed. The same

applies to all controls on the System Configuration panel. If one clicks on any of the State indicators during heating, the heating process will be terminated, and cooling will begin. Clicking on any of them during cooling will terminate the cooling process and restore the normal state. A typical appearance of the Main panel during a heat cycle is shown in Figure 4-2.

Figure 4-2 Appearance of the Main panel during a heat cycle. Only the heater controls and the State indicators can be operated while heating or cooling is in progress. Here the system is in the Master mode (see Section 4.2.8), and the channels are heated in groups of two.

If you are using a PCI-1000 unit, you may open a PCI panel by selecting MODULE > Show PCI. If you are using more than one PCI-1000 unit, a submenu offering choices for each unit will appear. From the PCI panels you may control all the settings pertaining to the PCI units, including the internal test signal generator and filter bank. Additionally, you may control which channel's signal is routed to the front panel BNC output connector. To hide a PCI panel, select

MODULE> Hide PCI, or (as with most windows encountered in the PCS102 Control Software) click on the standard Windows<sup>TM</sup> "close" button marked with an "×" in the upper right corner of the window.

## 4.2 Main Panel Functions

## 4.2.1 Main Panel Menu Items

FILE>About: Brings up the "About" panel which displays the version number of the software and lists the installed modules. Please note this information when contacting STAR Cryoelectronics for service. Left-click on this panel to hide it.

FILE>QUIT (hot-key Q): Quits the PCS102 Control Software. Alternatively, the "close" button ( $\times$ ) in the upper right corner of the Main panel can be used. All current settings are stored in the selected initialization file, and are restored when the software is run the next time.

CONF>Refresh (hot-key X): Used to re-send all current data and configuration settings to all the installed PFL-102 and PCI-1000 units. This is important to ensure or re-establish the equivalence of the software and hardware configurations. The REFRESH command should be used whenever power to the PCI unit has been turned on or whenever any of these units has been disconnected or the communication path has been interrupted. Alternatively, the REFRESH button in the Configuration section of the Main panel can be used.

CONF>Display: The items found in the sub-menu of this item may be used to show or hide various portions of the Main panel. This is convenient if you wish to conserve space on your display monitor.

CONF>System (hot-key Y): Brings up the System Configuration panel, which is used to configure the basic parameters of the system, such as the number of channels, type and number of PCI units.

MODULE>Show PCI (hot-key I; PCI-1000 only). Brings up PCI panel(s). If you have more than one PCI-1000 unit, a sub-menu appears which allows the selection of a particular PCI panel. If several PCI panels are displayed, a particular PCI panel can be selected using hot key Ctrl + panel number.

MODULE/Hide PCI (hot-key Alt + I; PCI-1000 only). This item closes the PCI panel(s). If more than one PCI-1000 unit is installed, a sub-menu appears offering a selection of PCI panels to hide. Alternatively, the OK button, or the "close" button (×) in the right upper corner of each PCI panel can be used.

## 4.2.2 Channel Controls

Select box: (hot-key Alt + number to select a channel from 1 to 9, Alt + N to select the next channel): Used to select a channel. Settings for this channel are then displayed in the Tune and Configuration sections of the Main panel.

ST / SL (hot keys T to tune and L to lock the input SQUID): The State indicator for the input SQUID. Click to toggle between the TUNE ("ST") and the LOCK ("SL") modes for the SQUID. The channel then becomes selected. If clicked during heating, the heat cycle will terminate and the cool cycle will begin, if clicked during cooling, the initial state will be restored.

AT / AL (hot keys Alt + T to tune and Alt + L to lock the array): The State indicator for the output array. Click to toggle between the TUNE ("AT") and the LOCK ("AL") modes for the array. The channel then becomes selected. If clicked during heating, the heat cycle will terminate and the cool cycle will begin, if clicked during cooling, the initial state will be restored.

## 4.2.3 Mode Controls

S-LOCK (hot-key L): Used to operate the input SQUID of the selected channel in the LOCK mode. The LOCK mode of the SQUID is indicated by a green State indicator with the "SL" abbreviation. Note that by locking the SQUID, one forces the array into the TUNE mode.

S-TUNE (hot-key T): Used to operate the input SQUID of the selected channel in the TUNE mode. In the TUNE mode, the feedback loop is open. This mode is used to adjust the SQUID operating parameters for optimal sensitivity and performance. The TUNE mode of the SQUID is indicated by a yellow State indicator with the abbreviation "ST".

A-LOCK (hot-key Alt + L): Used to operate the output array of the selected channel in the LOCK mode, indicated by a green State indicator with the abbreviation "AL". Note that by locking the array, one forces the SQUID into the TUNE mode.

A-TUNE (hot-key Alt + T): Used to operate the output array of the selected channel in the TUNE mode, indicated by a yellow State indicator with the abbreviation "AT".

RESET (hot-key R): Sends a RESET command to the selected channel. This action, which only has an effect while in the LOCK mode, temporarily opens the feedback loop and discharges the integrator. In this way, the PFL-102 may begin tracking the applied signal starting with a value as close to zero as possible.

HEAT (hot-key H): Initiates a heat and cool cycle for the selected channel. It may also be used during an ongoing heat cycle to restart it. The State indicators display the word "HE AT" during heating and the word "CO OL" during cooling.

## 4.2.4 Tune Parameter Controls

The tune parameter controls are S-BIAS, S-FLUX, A-BIAS, A-FLUX, and OFFSET. These controls are used to adjust the SQUID and array tune parameters to optimize performance. Each control operates an associated digital-to-analog converter in the PFL-102 unit. A hot key is assigned to each control. When the control is active, one can use the scroll arrows in the control window or the Up or Down arrow keys to adjust the displayed value. The COARSE / FINE control sets the step size, which is defined as a certain fraction of the maximum value for each control. The FINE setting corresponds to a single DAC bit, *i.e.*, the highest possible resolution. Additionally, one may simply type the desired value into the control and then press Enter. If the entered value is out of range, the value displayed is the nearest valid value. Below are descriptions of the individual controls. Note that one can learn about any control simply by right-clicking on the control.

S-BIAS (hot-key B): Sets the value of the SQUID bias current in milliamperes. The default maximum value for this control is 2.0 mA (the full-scale label can be changed by editing the SBIASMAX entry in the corresponding initialization file).

S-FLUX (hot-key F): Sets the value of the dc offset flux applied to the SQUID, specified in units of current (microamperes). This control may be used to offset the output signal while in the LOCK mode, or to adjust the offset of the flux sweep in the TUNE mode. The default maximum value for this control is 100  $\mu$ A (the full-scale label can be changed by editing the SFLUXMAX entry in the corresponding initialization file).

COARSE / FINE (for the SQUID; hot-key C): Sets the incremental step for the S-BIAS and S-FLUX controls. The FINE setting corresponds to the highest resolution. Click on this control to toggle its value.

ZERO / RESTORE (for the SQUID; hot-key Z): Sets the SQUID bias and flux to 0, while keeping in memory their original values. This is useful when connecting or disconnecting the PFL from the sensor, or during an initial cooldown of the sensor. Click on this control to zero the outputs (if not in "zero" state), or to restore them to the original values (if in "zero" state).

A-BIAS (hot-key Alt + B): Sets the value of the array bias current in microamperes. The default maximum value for this control is  $100 \ \mu A$  (the full-scale label can be changed by editing the ABIASMAX entry in the corresponding initialization file).

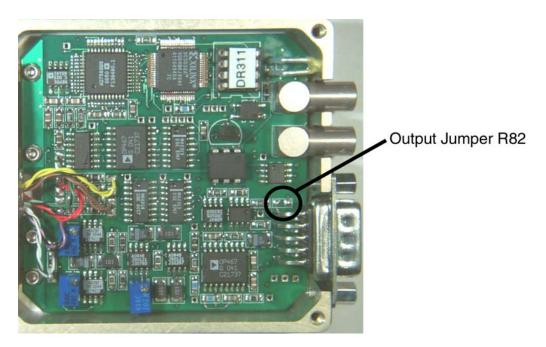

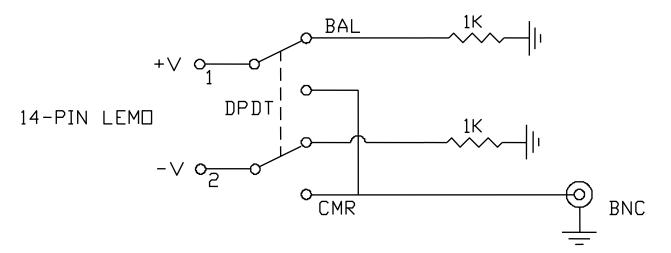

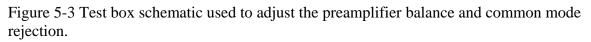

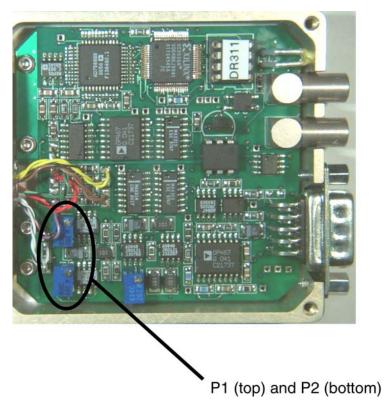

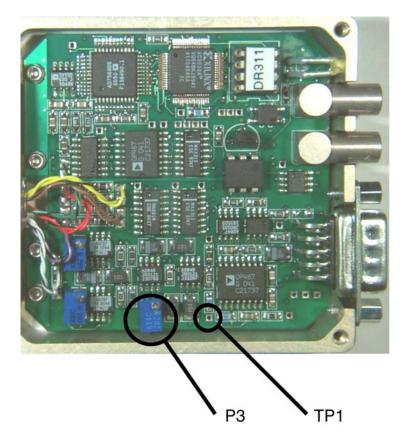

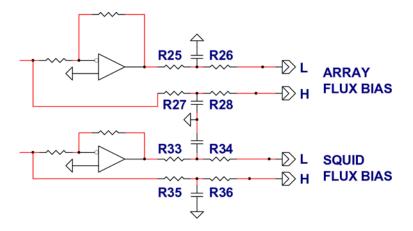

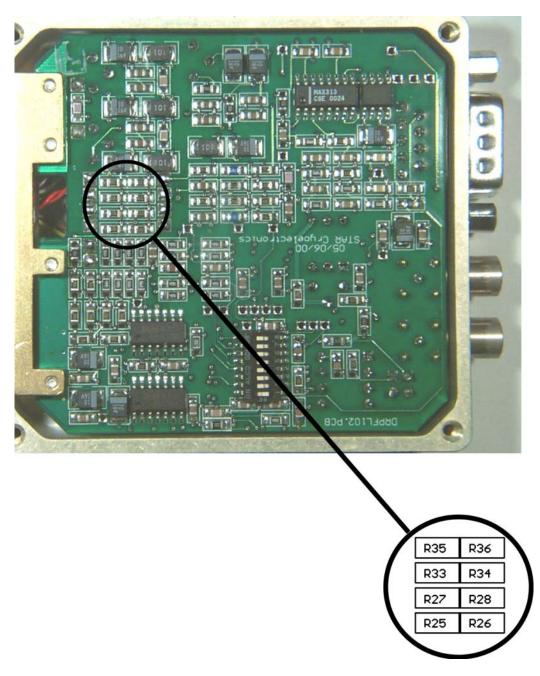

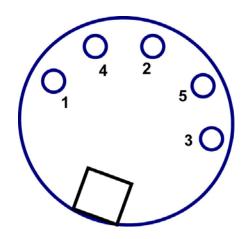

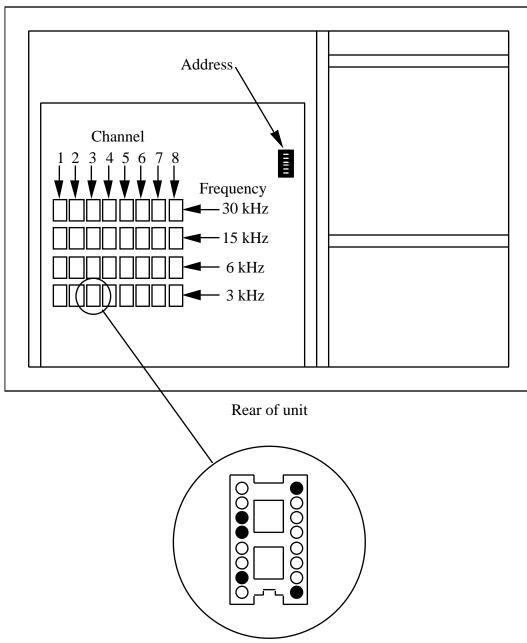

A-FLUX (hot-key Alt + F): Sets the value of the offset dc flux applied to the Array, specified in units of current (microamperes). The default maximum value for this control is 200  $\mu$ A (the full-scale label can be changed by editing the AFLUXMAX entry in the corresponding initialization file).